JEDEC JESD22-A200 Die ESD Human Body Model Testing

The JEDEC JESD22-A200 standard defines the test procedure for assessing the electrical characteristics of semiconductor devices under simulated human body model (HBM) electrostatic discharge (ESD). This service is crucial in the semiconductor and microchip testing sector as it ensures that devices are robust against ESD, which can cause significant damage during manufacturing, packaging, assembly, or handling.

The JESD22-A200 test simulates the ESD event by subjecting the die to a high-voltage discharge through a capacitor. The capacitor is charged and then discharged into the die at specific voltage levels (typically -4 kV, +4 kV). The objective is to measure the current flowing between the capacitor and the die during this process.

The testing parameters are critical for ensuring accurate results. A typical setup includes:

- Test voltage: -4 kV or +4 kV

- Capacitance of the discharge capacitor: 10 pF

- Waveform: a triangular waveform with a rise time of 50 ns and fall time of 2.5 µs

- Measurement parameters: current, voltage, and capacitance

The specimen preparation involves ensuring the die is in a stable state before testing. This includes:

- Cleaning the die surface to remove any contaminants that could affect test results.

- Securing the die on the tester's probe holder to ensure reliable contact during the test.

- Aging the die for 10 minutes at room temperature after cleaning and before testing.

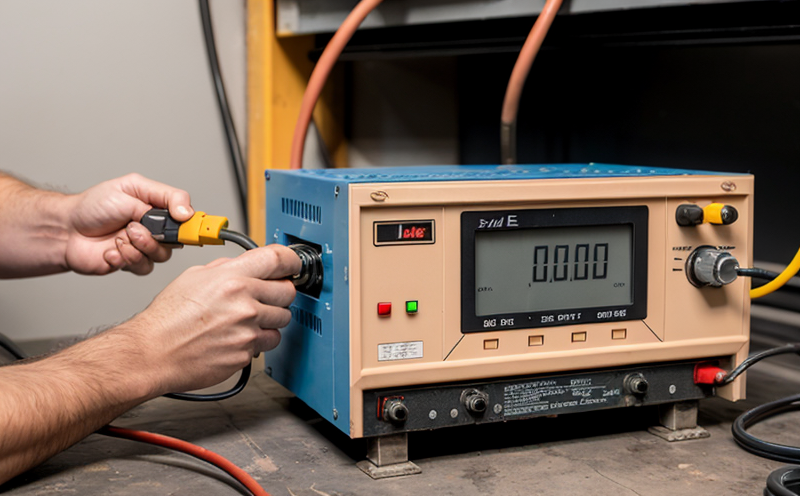

The instrumentation used in this process includes:

- An ESD tester capable of generating the specified discharge voltage and current measurements.

- High-precision probes to ensure accurate contact with the die during testing.

- Data acquisition systems that capture and analyze the test data.

The acceptance criteria for this test involve:

- No more than 10 µA of leakage current at the specified voltage levels.

- No damage to the die as evidenced by visual inspection or functional tests post-testing.

In real-world applications, this testing is used to ensure that semiconductor devices are reliable and robust against ESD events. This is particularly important in sectors where the handling of electronic components involves human contact, such as consumer electronics manufacturing, automotive electronics, and medical device production.

Failure to meet these criteria can lead to:

- Degradation of product performance

- Increased warranty claims due to premature failures

- Reputation damage for the manufacturer

The benefits of this testing include:

- Enhanced reliability of the final product

- Cost savings from reduced failure rates and warranty expenses

- Improved customer satisfaction through higher quality products

Our laboratory adheres to strict standards, ensuring that all tests are conducted in compliance with JEDEC JESD22-A200. We provide comprehensive reports detailing the test parameters, specimen preparation, instrumentation used, and final results.

| Parameter | Description |

|---|---|

| Test Voltage | -4 kV or +4 kV |

| Capacitance | 10 pF |

| Rise Time | 50 ns |

| Fall Time | 2.5 µs |

| Leakage Current | No more than 10 µA |

Scope and Methodology

The scope of the JEDEC JESD22-A200 die-level ESD testing includes:

- Testing semiconductor devices for their ability to withstand simulated human body model electrostatic discharge events.

- Ensuring compliance with relevant international standards such as JEDEC, ISO, and ASTM.

- Providing detailed reports that include test parameters, specimen preparation, instrumentation used, and final results.

The methodology for conducting this testing involves:

- Setting up the tester to generate the specified discharge voltage and current measurements.

- Cleaning the die surface before securing it on the probe holder.

- Aging the die for 10 minutes at room temperature.

- Performing the ESD test with a triangular waveform as described in the JESD22-A200 standard.

- Making the necessary measurements and recording the results.

- Evaluating the results against the acceptance criteria specified by JEDEC.

The test setup includes:

- An ESD tester capable of generating the specified discharge voltage and current measurements.

- High-precision probes to ensure accurate contact with the die during testing.

- Data acquisition systems that capture and analyze the test data.

In addition to the above, we also provide:

- Visual inspection of the die before and after testing to check for any visible damage.

- Functional tests post-testing to ensure there is no degradation in device performance.

- Detailed reports that include all test parameters, specimen preparation, instrumentation used, and final results.

The acceptance criteria for this test involve:

- No more than 10 µA of leakage current at the specified voltage levels.

- No damage to the die as evidenced by visual inspection or functional tests post-testing.

In real-world applications, this testing is used to ensure that semiconductor devices are reliable and robust against ESD events. This is particularly important in sectors where the handling of electronic components involves human contact, such as consumer electronics manufacturing, automotive electronics, and medical device production.

| Parameter | Description |

|---|---|

| Test Voltage | -4 kV or +4 kV |

| Capacitance | 10 pF |

| Rise Time | 50 ns |

| Fall Time | 2.5 µs |

| Leakage Current | No more than 10 µA |

Industry Applications

The JEDEC JESD22-A200 die-level ESD testing is widely used in the semiconductor and microchip testing sector. Some of the key applications include:

- Consumer electronics manufacturing: Ensuring that devices are robust against human body model electrostatic discharge events.

- Automotive electronics: Protecting sensitive components from potential damage during assembly and handling.

- Medical device production: Guaranteeing the reliability of electronic components in critical applications.

The testing process is also used to:

- Enhance product quality by ensuring that devices are robust against ESD events.

- Reduce warranty claims due to premature failures caused by ESD damage.

- Improve customer satisfaction through higher quality products.

In addition, this testing is used in:

- Research and development: Identifying areas for improvement in the design of semiconductor devices.

- Procurement: Ensuring that components meet stringent reliability standards before being incorporated into final products.

The benefits of this testing include:

- Enhanced reliability of the final product.

- Cost savings from reduced failure rates and warranty expenses.

- Improved customer satisfaction through higher quality products.

In real-world applications, this testing is used to ensure that semiconductor devices are reliable and robust against ESD events. This is particularly important in sectors where the handling of electronic components involves human contact, such as consumer electronics manufacturing, automotive electronics, and medical device production.