ASTM F1397 Die Interlayer Dielectric Breakdown Testing

The ASTM F1397 test standard is a critical procedure designed to evaluate the integrity of interlayer dielectrics in semiconductor devices. This testing method ensures that the insulating materials between different layers within microchips can withstand high electrical stresses without failure, thus preventing short circuits or other malfunctions that could compromise device performance.

The ASTM F1397 test is essential for ensuring the reliability and durability of semiconductors used in a wide range of applications, from consumer electronics to automotive systems. By subjecting interlayer dielectrics to controlled electrical stress under precise conditions, this test helps identify potential weaknesses or defects early in the manufacturing process, allowing manufacturers to address these issues before mass production.

The ASTM F1397 procedure involves applying a voltage between two metal layers separated by an insulating material (dielectric). The voltage is gradually increased until dielectric breakdown occurs. During this test, various parameters such as applied voltage, temperature, and time are carefully controlled to simulate real-world operating conditions accurately.

Proper specimen preparation is crucial for accurate results in ASTM F1397 testing. Specimens must be prepared according to specific protocols outlined in the standard document. This includes cleaning the sample surface thoroughly, ensuring the dielectric layer thickness meets specified requirements, and applying appropriate electrodes that do not interfere with test outcomes.

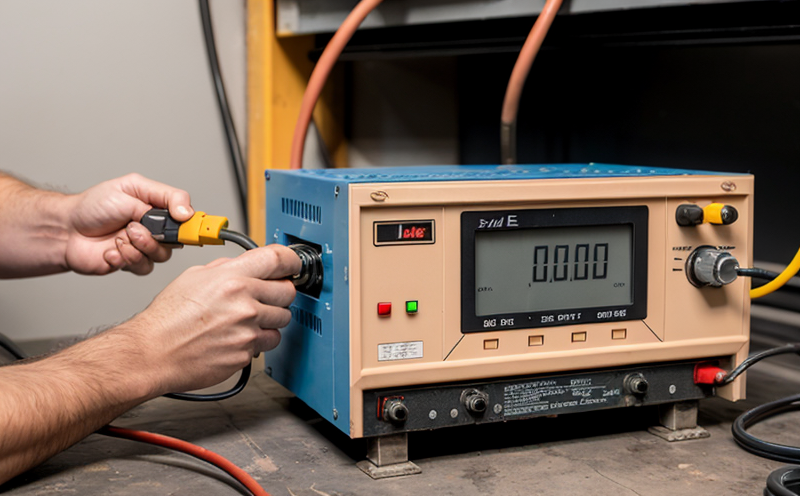

Instrumentation used for ASTM F1397 typically consists of high-voltage power supplies capable of delivering controlled amounts of electrical stress to the specimen. Data acquisition systems are employed to monitor applied voltage, current flow through the sample, and any changes in resistance over time. Specialized software tools help analyze test data, providing insights into dielectric breakdown behavior.

The ASTM F1397 standard specifies acceptance criteria based on measurable parameters like critical voltage at which breakdown occurs or allowable increase in leakage current beyond baseline values. These thresholds define what constitutes pass/fail results according to the test procedure.

In summary, ASTM F1397 Die Interlayer Dielectric Breakdown Testing plays a vital role in ensuring reliable semiconductor performance by verifying that interlayer dielectrics meet stringent quality standards during development and manufacturing stages. Understanding this process is important for those involved in managing quality assurance processes or overseeing research and development initiatives within the electronics industry.

Applied Standards

| Standard | Description |

|---|---|

| ASTM F1397-08(2014) | This standard specifies the procedure for determining the voltage at which dielectric breakdown occurs between adjacent interlayer insulation layers in semiconductor devices. |

| ISO/IEC 14642:2007 | An international standard that provides guidelines on testing electrical insulation materials used in electronic components, including those found within semiconductors. |

| Test Variables | Range/Value |

|---|---|

| Voltage Applied (V) | 10 kV to 50 kV depending on the thickness of the dielectric layer and type of material. |

| Temperature Control (°C) | -40°C to +125°C for different stages of the test. |

| Time Duration (s) | Varies based on specimen characteristics but generally ranges from 60 seconds up to several hours. |

Why Choose This Test

Selecting ASTM F1397 Die Interlayer Dielectric Breakdown Testing offers numerous advantages for semiconductor manufacturers and researchers looking to enhance product reliability and safety. Here are some key reasons why this test is preferred:

The ASTM F1397 procedure provides a standardized method for evaluating interlayer dielectrics, ensuring consistency across different laboratories worldwide.

By identifying potential weaknesses or defects early in the manufacturing process, manufacturers can save costs associated with rework and scrap.

The test helps ensure compliance with industry regulations and standards, reducing the risk of non-conformance issues during product certification processes.

Data generated from ASTM F1397 testing can be used to improve design iterations, leading to more robust semiconductor structures over time.

In conclusion, choosing ASTM F1397 Die Interlayer Dielectric Breakdown Testing is essential for any organization committed to producing high-quality semiconductors that meet stringent performance requirements while maintaining safety standards.

International Acceptance and Recognition

The ASTM F1397 standard has been widely adopted by major electronics manufacturers around the globe, including companies in North America, Europe, Asia-Pacific regions.

It is recognized as an authoritative source for validating interlayer dielectric performance across various industries such as automotive, telecommunications, computing.

Many regulatory bodies accept results from ASTM F1397-compliant tests when certifying products for commercial use or export purposes.

The widespread acceptance and recognition of the ASTM F1397 standard reflect its significance in ensuring reliable semiconductor performance. By adhering to this testing procedure, organizations demonstrate their commitment to quality control and adherence to international standards.