JEDEC JESD22-A114 Die Electrostatic Discharge Testing

The JEDEC JESD22-A114 standard is a critical procedure used to evaluate the electrostatic discharge (ESD) robustness of semiconductor dies. This testing ensures that semiconductors can withstand high-energy discharges without suffering damage, thus maintaining their functionality and reliability.

Electrostatic Discharge (ESD) refers to sudden electrical currents generated by a static charge. These charges are typically caused by friction or contact between materials, such as human hands handling electronic components. In semiconductor manufacturing, ESD can occur during various stages of production, packaging, and handling, posing significant risks to the integrity of sensitive electronic parts.

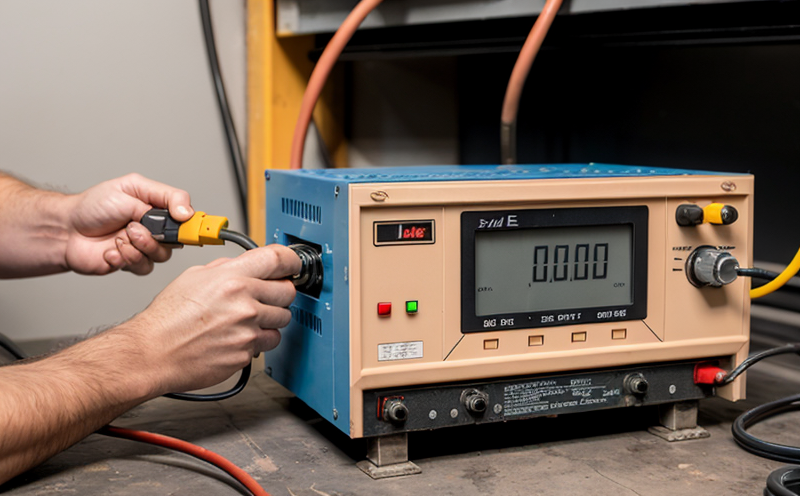

The JEDEC JESD22-A114 standard defines a series of test conditions that simulate the real-world scenarios where ESD may occur. The test involves applying a controlled amount of current through the die in various configurations to observe its response under different stress levels. This process helps manufacturers and quality assurance teams identify potential weaknesses early, allowing for corrective actions before mass production.

The standard covers several key parameters that are critical for ensuring accurate testing results:

- Test voltage levels

- Dwell time (the duration the discharge is applied)

- Number of test iterations

- Die orientation during testing

To achieve reliable and repeatable test results, it is essential to adhere strictly to these parameters. Compliance with JESD22-A114 ensures that the tested components meet industry standards for ESD robustness.

The testing process involves several steps:

- Preparation of the die on a suitable substrate

- Attachment of electrodes for voltage application

- Application of controlled discharge pulses

- Data collection and analysis

- Evaluation against specified criteria

The results from this testing are crucial for ensuring that semiconductor dies can handle the static charges they may encounter during manufacturing, packaging, or even in end-user environments. By adhering to JESD22-A114 standards, manufacturers can enhance product reliability and customer satisfaction.

| Test Parameter | Description |

|---|---|

| Test Voltage (kV) | Ranges from 3 kV to 5 kV depending on the die type |

| Dwell Time (ms) | Duration of discharge, typically between 1 ms and 20 ms |

| Number of Iterations | Multiple test cycles to ensure consistent results |

| Die Orientation | Different orientations are tested for comprehensive coverage |

The testing process is not only about identifying failures but also about understanding the root cause of any issues. This knowledge allows manufacturers to improve their processes and materials, thereby enhancing product quality.

For quality managers and compliance officers, ensuring compliance with JESD22-A114 is crucial for maintaining a high standard of product integrity. R&D engineers can use this testing to innovate and refine die design and manufacturing techniques. Procurement teams benefit from knowing that the components they source are rigorously tested according to industry standards.

In summary, JEDEC JESD22-A114 Die Electrostatic Discharge Testing is a vital step in semiconductor quality assurance. It ensures that dies can withstand ESD without damage, thereby enhancing product reliability and customer trust. This testing aligns with international standards, ensuring uniformity across the industry.

Scope and Methodology

The scope of JEDEC JESD22-A114 testing includes a comprehensive evaluation of semiconductor dies under controlled ESD conditions to ensure robustness. The methodology involves several key steps:

- Test Setup: Preparation of the die on a suitable substrate with electrodes attached for voltage application.

- Voltage Application: Controlled discharge pulses are applied at specified voltages and dwell times.

- Data Collection: Detailed recording of test results, including pass/fail criteria.

- Evaluation: Analysis of data to determine compliance with JESD22-A114 standards.

The methodology is designed to simulate real-world ESD conditions, ensuring that the tested components are prepared for actual use. Compliance with these standards ensures high reliability and robustness of semiconductor dies in various applications.

| Test Parameter | Description |

|---|---|

| Voltage (kV) | 3 kV to 5 kV, depending on die type |

| Dwell Time (ms) | 1 ms to 20 ms |

| Number of Iterations | Multiple cycles for consistent results |

| Die Orientation | Different orientations tested to cover all angles |

This testing ensures that semiconductor dies can withstand the static charges they may encounter during manufacturing, packaging, and handling. The methodology is carefully designed to provide accurate and reliable results.

Industry Applications

- Aerospace & Defense: Ensures reliability in harsh environments where ESD can cause significant issues.

- Automotive: Critical for components that must operate in high-voltage conditions without failure.

- Consumer Electronics: Guarantees durability and longevity of consumer products against accidental static discharges.

- Data Centers: Important for the reliability of server components, ensuring continuous operation.

The JEDEC JESD22-A114 standard is widely recognized in industries where ESD robustness is critical. This testing ensures that semiconductor dies are prepared to handle static charges they may encounter throughout their lifecycle. The real-world applications highlight the importance of this testing for ensuring product reliability and customer satisfaction.

International Acceptance and Recognition

The JEDEC JESD22-A114 standard is internationally recognized, widely adopted by manufacturers and quality assurance teams globally. Compliance with this standard ensures that semiconductor dies are robust against ESD, thereby enhancing product reliability.

ISO/IEC: The JEDEC JESD22-A114 standard aligns closely with international standards, ensuring uniformity across the industry. This alignment helps manufacturers and users to achieve consistent results.

The widespread adoption of this testing procedure reflects its importance in maintaining high-quality semiconductor products. By adhering to these standards, manufacturers can ensure that their components meet the highest quality benchmarks.