JEDEC JESD22-A115 Die Input/Output Capacitance Testing

The JEDEC JESD22-A115 test method is a critical procedure for semiconductor and microchip manufacturing, ensuring the reliability and performance of die-level electrical components. This test evaluates the capacitance at the input and output terminals of integrated circuits (ICs) to ensure that they meet specified standards and perform as expected in real-world applications.

Capacitance is an essential parameter for determining how effectively a die can handle signals, manage power consumption, and minimize signal integrity issues. In semiconductor manufacturing, understanding capacitance at the die level helps quality managers, compliance officers, R&D engineers, and procurement teams ensure that their products meet industry standards without compromising performance.

The test involves measuring the capacitance of each input/output (I/O) pin on a die to identify any discrepancies from expected values. This process is crucial for ensuring that the die can handle signals without excessive noise or energy loss. The testing procedure is standardized, making it an indispensable part of quality control and compliance.

The JESD22-A115 test method is widely used across various sectors, including consumer electronics, automotive, medical devices, and industrial equipment. By ensuring that each die meets the specified capacitance requirements, manufacturers can enhance product reliability and reduce the risk of field failures. This testing ensures that semiconductor components perform reliably under a wide range of operating conditions.

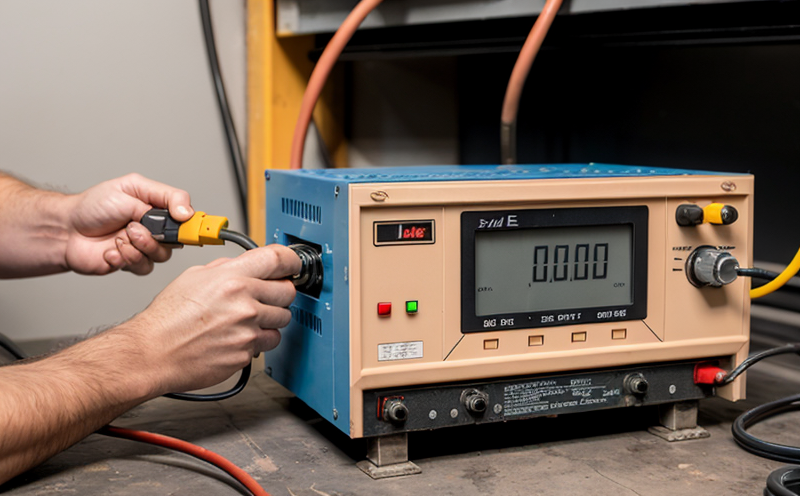

The JEDEC JESD22-A115 test is typically performed using specialized test equipment designed to measure very small capacitances accurately. The process involves connecting the die to a test fixture, applying a known voltage, and measuring the resulting current to calculate the capacitance. This method ensures that even slight variations in capacitance are detected.

Die-level testing is particularly important for ensuring that each individual component within an integrated circuit meets the required specifications. By identifying any discrepancies early in the manufacturing process, manufacturers can address issues before they become costly problems downstream. This approach also helps to ensure compliance with international standards such as JEDEC JESD22-A115.

The test results are typically reported in terms of capacitance values for each I/O pin, along with any deviations from the specified limits. These reports provide critical information to quality managers and R&D engineers, allowing them to make informed decisions about product design and manufacturing processes.

| Applied Standards |

|---|

| JESD22-A115: Die-Level Electrical and Functional Testing |

The JEDEC JESD22-A115 test method is a recognized standard for evaluating the capacitance of die-level I/O pins. This test ensures that each individual component within an integrated circuit meets the required specifications, enhancing product reliability and reducing the risk of field failures.

Applied Standards

The JEDEC JESD22-A115 test method is based on international standards that ensure the electrical performance of semiconductor devices. The primary standard used in this testing procedure is:

| Standard | Description |

|---|---|

| JESD22-A115: Die-Level Electrical and Functional Testing | This standard provides detailed procedures for evaluating the electrical characteristics of die-level components, including capacitance at I/O pins. It ensures that each component meets specified performance criteria to enhance overall product reliability. |

The JESD22-A115 test method is widely recognized and used in semiconductor manufacturing to ensure compliance with international standards and industry best practices.

Benefits

- Enhanced Product Reliability: By accurately measuring capacitance at the die level, manufacturers can identify potential issues early in the production process, reducing the risk of field failures and improving overall product reliability.

- Compliance with Industry Standards: The JEDEC JESD22-A115 test ensures that semiconductor devices meet specified performance criteria, facilitating compliance with international standards such as JEDEC JESD22-A115.

- Improved Signal Integrity: Measuring capacitance at the die level helps ensure that signals are transmitted accurately and without excessive noise or energy loss, enhancing overall signal integrity.

Customer Impact and Satisfaction

- Increased Confidence in Quality: By ensuring that each die meets the specified capacitance requirements, manufacturers can provide customers with confidence in the quality of their products.

- Reduced Field Failures: Early detection of discrepancies through die-level testing helps to reduce the risk of field failures, leading to higher customer satisfaction and loyalty.

- Better Product Design: The results from die-level capacitance testing can be used by R&D engineers to refine product design, ensuring that future generations of products meet even stricter performance criteria.