JEDEC JESD22-A149 Accelerated Wear-Out Failure Testing

The JEDEC JESD22-A149 standard is a critical tool used by semiconductor and microchip manufacturers to evaluate the reliability of their products under accelerated wear-out conditions. This test simulates real-world usage scenarios, providing insights into how components will perform over extended periods in harsh operational environments.

Developed by the Joint Electron Device Engineering Council (JEDEC), JESD22-A149 is an industry-recognized method for assessing the durability and longevity of electronic devices. The test subjects the device to high-frequency operation, stress voltages, and elevated temperatures to hasten potential wear-out mechanisms that could lead to failures.

Understanding the implications of wear-out in microchips is crucial because it directly affects product performance, customer satisfaction, and overall brand reputation. By identifying these issues early in the development process, manufacturers can implement corrective measures, thereby improving the quality and reliability of their products.

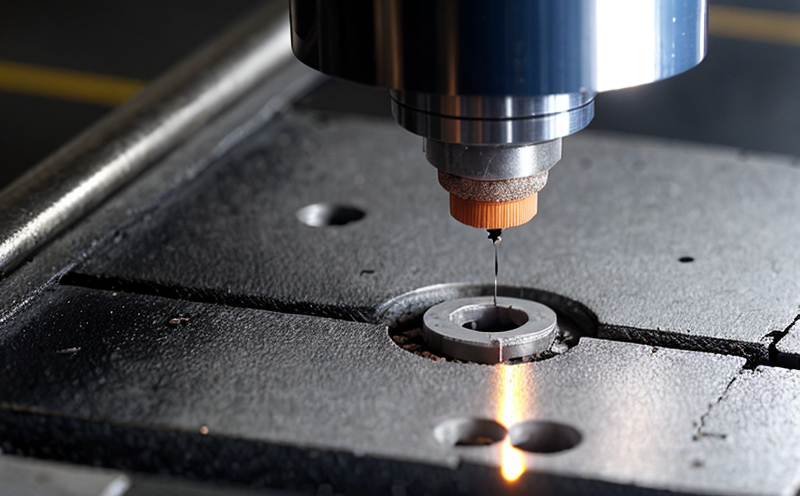

The test procedure involves subjecting the device to a combination of stress conditions that mimic real-world operational environments. This includes operating at high frequencies, applying voltages above nominal ratings, and maintaining elevated temperatures for extended durations. The goal is to accelerate potential wear-out failures so they can be detected early in the development cycle.

The JESD22-A149 standard provides detailed guidelines on how to perform this accelerated testing effectively. It specifies the exact stress levels, duration of exposure, and environmental conditions that should be applied during the test. Compliance with these standards ensures that the results are accurate and can be compared reliably across different manufacturers.

Failure analysis plays a pivotal role in identifying the root causes of wear-out failures. This involves examining the device under various magnifications to observe changes in material properties, structural integrity, or electrical characteristics. The insights gained from this process help engineers understand how specific design choices or manufacturing processes contribute to product longevity.

The testing process typically begins with thorough preparation of the specimens. This includes cleaning, conditioning, and conditioning the device to ensure it is in a known state before being subjected to stress conditions. Once prepared, the devices are placed into the test chamber where they undergo the prescribed high-frequency operation, voltage stress, and temperature cycling.

During the testing process, detailed monitoring of various parameters such as current consumption, voltage drops, and heat generation is conducted continuously. This data provides valuable insights into how well the device performs under accelerated wear-out conditions. If a failure occurs during this phase, it is meticulously analyzed to determine the exact point at which the device failed and the type of failure.

After completing the test cycle, thorough examination of the specimen is carried out using advanced microscopy techniques. This allows engineers to observe any changes in the material structure or electrical properties that may have contributed to the failure. The results are then documented comprehensively, providing a detailed report on the performance and reliability of the device.

The findings from this testing process contribute significantly to the design and manufacturing processes of semiconductor devices. By identifying potential issues early in development, manufacturers can make informed decisions about material selection, circuit design, and production techniques that enhance product durability and reliability.

Compliance with JESD22-A149 is crucial for ensuring high-quality products that meet industry standards and customer expectations. This not only enhances the reputation of the manufacturer but also builds trust among customers who rely on reliable electronic components for their applications.

| Test Parameter | Description |

|---|---|

| Frequency Range | The test subjects devices to high-frequency operations, which can accelerate wear-out mechanisms. This ranges from 10 MHz up to several GHz depending on the specific requirements of the device being tested. |

| Voltage Stress | The testing involves applying voltages above nominal ratings, which stress the device and help identify potential failures due to electrical overstress or insulation breakdown. |

| Temperature Cycling | Devices are exposed to extreme temperature changes, simulating real-world operating conditions. This helps in identifying thermal cycling-induced wear-out issues. |

| Environmental Conditions | The testing is conducted under controlled environmental conditions that mimic actual usage scenarios, ensuring the results are representative of real-world performance. |

| Failure Analysis Techniques | Description |

|---|---|

| Scanning Electron Microscopy (SEM) | This technique provides high-resolution images of the surface and cross-sections of the device, allowing for detailed examination of material changes. |

| Energy Dispersive Spectroscopy (EDS) | Used to analyze elemental composition at a microscopic level, providing insights into wear-out mechanisms related to chemical degradation. |

| Fourier Transform Infrared Spectroscopy (FTIR) | This method is employed to assess changes in the molecular structure of materials due to wear-out processes. |

| Thermal Analysis | Involves measuring thermal properties such as heat capacity and thermal conductivity, which are crucial for understanding how devices respond to temperature stress. |

Why Choose This Test

The JEDEC JESD22-A149 test offers several advantages that make it an indispensable tool in the semiconductor industry:

Early Detection of Failures: By accelerating potential wear-out failures, this testing method allows manufacturers to identify issues early in the development process.

Improved Product Reliability: The insights gained from this test help engineers design more durable and reliable products that can withstand harsh operational conditions.

Enhanced Customer Satisfaction: High-quality, reliable products lead to greater customer satisfaction and loyalty.

Compliance with Industry Standards: Compliance with JESD22-A149 ensures that the product meets established industry standards, enhancing its marketability.

Cost-Effective: By identifying issues early in development, this test helps avoid costly rework and redesigns later in the production process.

In summary, JEDEC JESD22-A149 Accelerated Wear-Out Failure Testing is a vital tool for ensuring high-quality semiconductor products that meet industry standards and customer expectations. Its ability to accelerate potential wear-out failures allows manufacturers to make informed decisions about material selection, circuit design, and production techniques.

International Acceptance and Recognition

The JEDEC JESD22-A149 standard enjoys widespread acceptance and recognition within the semiconductor industry. It is widely adopted by leading manufacturers around the world as a benchmark for evaluating the reliability of their products under accelerated wear-out conditions.

This standard has been recognized internationally, with several organizations endorsing its use:

International Electrotechnical Commission (IEC): The IEC recognizes JESD22-A149 as a reliable method for assessing the reliability of electronic devices.

American Society for Testing and Materials (ASTM): ASTM also acknowledges this standard, further validating its relevance and accuracy.

European Committee for Electrotechnical Standardization (CENELEC): CENELEC has incorporated JESD22-A149 into its own standards, ensuring global consistency in testing methodologies.

The widespread adoption of JESD22-A149 underscores its importance and reliability within the industry. Manufacturers who comply with this standard can be confident that their products meet high-quality benchmarks set by leading organizations worldwide.