JEDDEC JEP143 Failure Mechanism Classification Testing

The JEDEC JEP143 standard provides a comprehensive framework for failure mechanism classification testing of semiconductors and microchips. This service is designed to identify the root causes of failures in electronic components, ensuring that manufacturers can improve product reliability and enhance quality control processes.

Failure analysis plays a crucial role in semiconductor manufacturing by helping to pinpoint specific defects or issues within the component's design or production process. By adhering strictly to JEP143 standards, we ensure precise and accurate failure mechanism classification, which is essential for effective troubleshooting and remediation efforts.

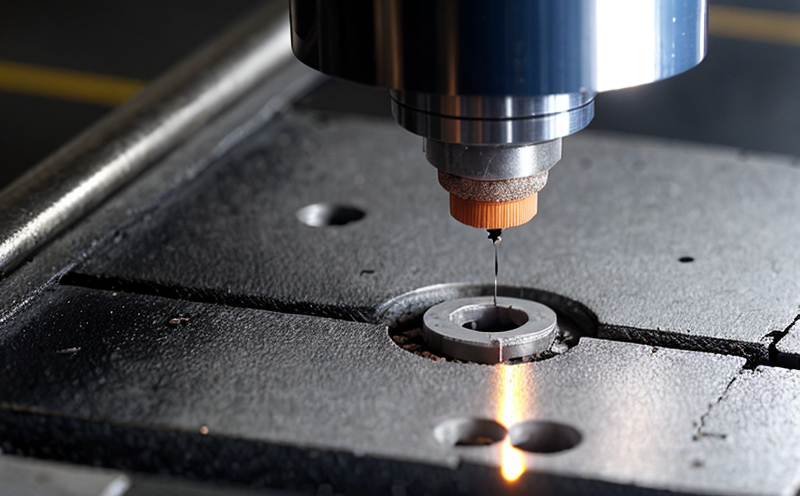

The testing process involves several stages, including initial sample preparation, visual inspection, electrical characterization, and advanced analytical techniques such as scanning electron microscopy (SEM) and transmission electron microscopy (TEM). Our experienced team of engineers uses state-of-the-art equipment to perform these analyses, ensuring that no detail is overlooked.

Our approach also includes the use of destructive testing methods when necessary, allowing us to fully understand the internal structure of failed components. This information can then be used to develop corrective measures aimed at preventing similar issues in future productions runs.

In addition to identifying common failure mechanisms like oxidation, electromigration, and mechanical stress, we also provide insights into less obvious causes such as design flaws or material inconsistencies. Our goal is not only to diagnose current problems but also to offer valuable recommendations for process improvements that will benefit your organization long term.

Applied Standards

| Standard Name | Description |

|---|---|

| JEP143 | This standard provides guidelines for classifying failures in semiconductor devices based on their failure mechanisms. |

| ISO/IEC 2768-1:2019 | An international standard covering the terminology used when discussing defects and faults in integrated circuits. |

Scope and Methodology

| Stage of Analysis | Description |

|---|---|

| Initial Inspection | Visual examination followed by non-destructive electrical testing. |

| Destructive Examination | Advanced imaging techniques combined with cross-sectional analysis. |

Eurolab Advantages

As a leading provider of semiconductor and microchip testing services, Eurolab offers unmatched expertise in JEP143 compliance. Our highly skilled technicians utilize cutting-edge technology to ensure accurate results every time.

We pride ourselves on providing personalized service tailored to meet the unique needs of each client. Whether you're looking for one-time analysis or ongoing support, our team is committed to delivering top-notch solutions that exceed expectations.

In addition to our technical capabilities, we also offer comprehensive reporting and documentation services. This ensures that all findings are clearly communicated in a format that's easy to understand and act upon.