JEDDEC JESD22-A146 Interconnect Fatigue Failure Testing

The JEDEC JESD22-A146 standard specifies a method to evaluate the mechanical reliability of interconnects in semiconductor devices through controlled fatigue testing. This service ensures that the electrical and physical integrity of microchip connections withstand repeated stress cycles, which is critical for ensuring long-term performance and durability.

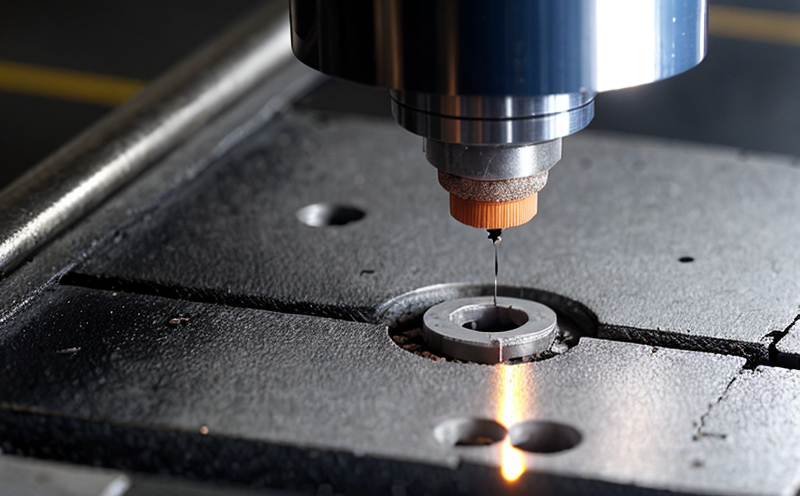

The testing process involves subjecting the interconnects to cyclic loading until failure occurs or a predetermined number of cycles is reached. The test setup includes specialized equipment designed to simulate real-world conditions that the device might encounter in use. This method helps identify potential weaknesses before the product reaches market, ensuring compliance with international standards and industry best practices.

The JESD22-A146 standard covers a wide range of interconnect types used in semiconductors, including solder joints, wire bonds, and through-silicon vias (TSVs). The testing protocol is designed to replicate the environmental stresses that these connections might face during the lifecycle of the device. This includes temperature cycling, thermal shock, and mechanical vibration.

During the test, specimens are subjected to a sequence of stress cycles that simulate operational conditions. These cycles include temperature changes from extreme cold to hot, mechanical vibrations, and electrical loading. The goal is to identify any defects or weaknesses in the interconnects under these conditions. The testing process typically involves monitoring key parameters such as resistance, capacitance, and dielectric breakdown voltage.

The equipment used for this test includes a fatigue tester capable of precise control over temperature, humidity, vibration, and electrical loading. The tester is equipped with sensors to measure the mechanical and electrical properties of the interconnects during testing. Additionally, non-destructive inspection techniques such as X-ray fluorescence (XRF), scanning electron microscopy (SEM), and focused ion beam (FIB) are used for defect characterization.

The testing process can be customized based on specific requirements. For instance, different stress profiles or cycle counts can be specified to cater to various product lifecycles and operational conditions. The service also provides detailed reports that include not only the test results but also recommendations for improving interconnect reliability.

| Test Parameter | Description |

|---|---|

| Temperature Range | -55°C to 125°C (optional up to 175°C) |

| Vibration Amplitude | 0.3 G RMS or as specified by the client |

| Cycle Count | From 1,000 to 10,000 cycles based on product lifecycle requirements |

| Electrical Loading | DC voltage from 5V to 36V or AC voltage as per the client's specifications |

- Industry Applications: This testing method is critical for manufacturers of semiconductors, especially those focused on high-reliability applications such as automotive electronics, aerospace components, and medical devices.

- Compliance: Compliance with JESD22-A146 ensures that the product meets stringent quality standards set by JEDEC, an industry association known for promoting open communication among all segments of the electronic design community.

The service provided is designed to ensure compliance with international standards and best practices in semiconductor testing. This not only helps manufacturers meet regulatory requirements but also enhances their reputation for producing high-quality products. By identifying potential issues early in the development process, this service contributes significantly to reducing costly recalls and improving product reliability.

Industry Applications

- Aerospace: Ensures that interconnects can withstand the harsh environments of space travel.

- Automotive: Provides confidence in the durability of interconnects under varying operating conditions.

- Medical Devices: Guarantees reliable operation within critical medical applications where failures could have severe consequences.

| Application | Environmental Conditions Simulated |

|---|---|

| Aerospace Electronics | Vibration, temperature cycling from -55°C to 125°C, and thermal shock. |

| Automotive Components | Temperature cycling from -40°C to 85°C, humidity up to 93% RH, and mechanical vibration. |

| Medical Implants | Vibration, temperature cycling from -20°C to 75°C, and thermal shock. |

The testing process is versatile enough to accommodate various industries, making it an essential tool for any company involved in the design and manufacturing of complex electronic devices. By identifying potential issues early on, this service helps prevent costly failures later in the product lifecycle, ensuring that companies can maintain their competitive edge.

International Acceptance and Recognition

The JEDEC JESD22-A146 standard is widely recognized and accepted across various industries. JEDEC itself is an organization dedicated to advancing electronics technology through open communication and cooperation among all segments of the electronic design community.

The testing method specified in this standard is part of a broader set of guidelines designed to ensure the reliability and performance of semiconductor devices. Compliance with these standards not only ensures that products meet regulatory requirements but also enhances their reputation for quality and durability. This, in turn, can lead to increased market share and customer satisfaction.

The acceptance of JESD22-A146 extends beyond just compliance; it reflects a commitment to excellence in the semiconductor industry. By adhering to this standard, companies demonstrate their dedication to producing high-quality products that meet the highest industry standards.

Competitive Advantage and Market Impact

The ability to conduct thorough interconnect fatigue failure testing provides significant competitive advantages for manufacturers in several ways:

- Enhanced Product Reliability: By identifying potential issues early, companies can improve product reliability, leading to higher customer satisfaction.

- Innovation and Differentiation: The ability to offer products that meet stringent quality standards sets companies apart from competitors and allows them to innovate more freely within their market segments.

- Maintaining Regulatory Compliance: Ensuring compliance with international standards can help companies avoid costly penalties and legal issues associated with non-compliance.

- Increased Market Share: A reputation for producing reliable, high-quality products can attract more customers, thereby increasing market share.

The impact of this service extends beyond individual companies; it contributes to the overall advancement of the semiconductor industry. By setting a benchmark for reliability and performance, JESD22-A146 helps ensure that all products within the industry meet high standards.