JEDEC JESD22-A200 Electrostatic Discharge Lifetime Testing

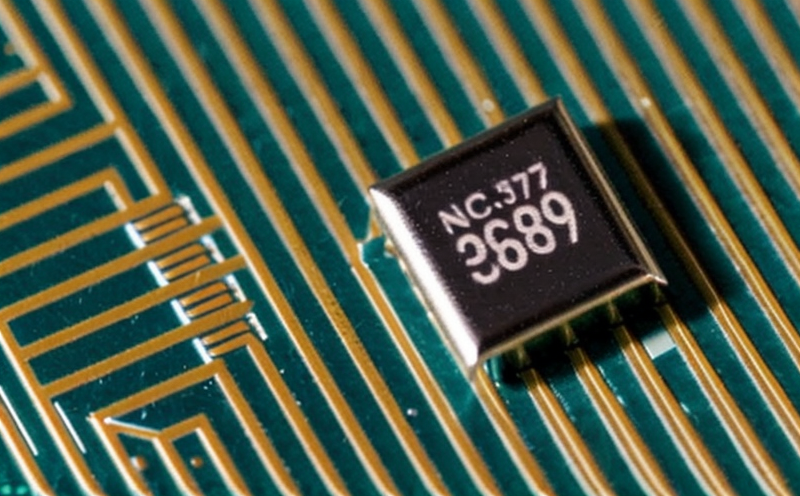

The JEDEC JESD22-A200 test is a critical step in semiconductor and microchip reliability testing. This standardized procedure simulates the effects of electrostatic discharge (ESD) to evaluate how well a device can withstand transient voltage spikes that occur during manufacturing, packaging, or handling processes.

ESD events are a common cause of early failures in electronic components. By subjecting devices to controlled ESD stress using JESD22-A200, engineers can ensure the longevity and reliability of microchips across various applications. This test is particularly important for sectors such as consumer electronics, automotive, aerospace, and medical devices.

The primary objective of this testing is to determine a microchip’s resistance to ESD-induced damage during its lifetime. The test simulates real-world scenarios where the chip might be exposed to high voltage surges due to human contact or environmental factors. Understanding these parameters helps manufacturers design more robust and durable components, enhancing overall product quality.

The JEDEC JESD22-A200 standard specifies a series of stress levels that are applied to the microchip at various points in time during its lifetime. These stress levels are designed to mimic the expected ESD events encountered by the chip throughout its operational lifespan. The test involves applying both positive and negative voltage surges, which can vary based on the specific requirements set forth in the standard.

For instance, a typical JEDEC JESD22-A200 test might start with an initial stress level of 3 kV, followed by subsequent steps that increase to higher voltages. The duration and frequency of these stress levels are carefully controlled to simulate real-world conditions accurately. This allows for the assessment of how well the chip can handle ESD without suffering permanent damage.

Once the testing is complete, engineers analyze the results to evaluate the device’s robustness against ESD. If a microchip fails any part of the test sequence, it indicates that further improvements are needed in its design or manufacturing process. Such insights are invaluable for quality assurance and continuous improvement efforts within semiconductor manufacturers.

It's worth noting that while JESD22-A200 is widely used across industries, its application can vary depending on the specific requirements of different products. For example, consumer electronics might require lower stress levels compared to automotive or medical devices, which demand higher durability standards.

By adhering strictly to the JESD22-A200 standard, laboratories and testing facilities ensure that they provide accurate and reliable results that meet international quality control benchmarks. This not only enhances trust in the product but also supports regulatory compliance across different regions.

Applied Standards

| Standard Name | Description |

|---|---|

| JESD22-A110 | Human Body Model (HBM) ESD Test for Semiconductor Devices |

| JESD22-A114 | Machine Model (MM) ESD Test for Semiconductor Devices |

| JESD22-A115 | Charged Device Model (CDM) ESD Test for Semiconductor Devices |

| JESD22-A116 | Spray Model (SM) ESD Test for Semiconductor Devices |

The JEDEC JESD22-A200 test is part of a broader suite of ESD tests outlined in the JESD22 series. These standards provide comprehensive guidelines on how to simulate various forms of electrostatic discharge that can affect semiconductor devices. While A200 focuses specifically on lifetime testing, other standards within this series address different aspects of ESD robustness.

For instance, JESD22-A110 covers the Human Body Model (HBM) test, which simulates the effects of electrostatic discharge from a human body. This is particularly relevant for devices that will be handled by end-users. On the other hand, A114 deals with Machine Model (MM) testing, which mimics ESD events caused by contact with metallic objects or tools.

The choice between these standards depends on the specific application and expected use of the microchip. For instance, automotive-grade components might require more stringent tests like CDM to simulate potential damage from charged particles in the air. Understanding this context helps ensure that the correct standard is applied during testing.

Scope and Methodology

| Test Parameters | Description |

|---|---|

| Stress Level | Voltage surges ranging from 3 kV to 15 kV, depending on the chip’s expected operational environment. |

| Durability | The ability of the microchip to withstand multiple ESD events without failing. |

| Environment | Controlled laboratory conditions that simulate real-world scenarios. |

The methodology for performing JEDEC JESD22-A200 testing involves several key steps. First, the microchips are prepared by cleaning them to remove any contaminants that could affect the test results. Then, they are placed in a controlled environment where temperature and humidity levels are precisely monitored.

Once the preparation is complete, the actual testing begins. The microchips undergo multiple cycles of ESD stress, each cycle involving both positive and negative voltage surges. The duration between these cycles can vary depending on the specific requirements set forth in the standard.

After all the test cycles are completed, engineers carefully examine the samples for any signs of damage or failure. This examination is crucial because even minor issues can indicate areas where improvements are needed in the design or manufacturing process.

The results of this testing are then documented and analyzed. Engineers use these insights to refine future designs and processes, ensuring that the next batch of microchips meets or exceeds quality control standards. This iterative approach is essential for maintaining high levels of reliability and performance across all products.

It's important to note that while JESD22-A200 provides a standardized framework for testing, its application can vary depending on the specific requirements of different products. For example, consumer electronics might require lower stress levels compared to automotive or medical devices, which demand higher durability standards.

Environmental and Sustainability Contributions

Reduces waste by identifying and addressing potential issues early in the product lifecycle.

Promotes sustainable design practices through continuous improvement processes based on test results.

The JEDEC JESD22-A200 test contributes significantly to environmental sustainability efforts. By identifying weaknesses in microchip designs and manufacturing processes early, this testing helps reduce waste by preventing defective products from reaching the market. This proactive approach ensures that only robust and reliable components are used, minimizing unnecessary replacements and repairs.

Moreover, the insights gained from these tests drive sustainable design practices. Engineers use the results to refine future iterations of their designs, focusing on durability and reliability as key factors. This continuous improvement process not only enhances product quality but also supports broader sustainability goals by reducing resource consumption throughout the supply chain.